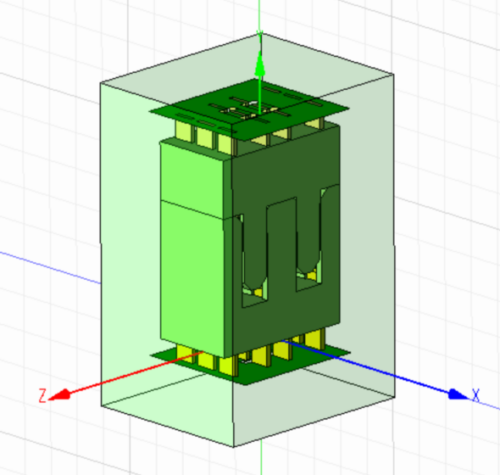

Advanced SI. Layout Workbench environment.

Fast Signal Integrity Analysis for PCB and Chip Packages

Key Advantages:

- Reduces cost and time by identifying potential crosstalk and crosstalk issues prior to fabrication

- Supports signal integrity verification using statistical analysis in the time and frequency domains of SerDes and parallel data buses from low frequencies up to 56 GHz.

Cadence® Sigrity™ Advanced SI helps you quickly implement signal integrity (SI) modeling of a complete data link from transmitter chip to receiver chip of typical interfaces in multiple modes:

- Synchronous output of signals for parallel buses

- Analysis of serial interfaces using transmitter pre- and post-emphasis (SerDes)

- Possibility of flexible configuration of the data transmission channel with the ability to simulate signal integrity, taking into account the real influence of the power system or with an idealized power supply

Sigrity Topology Explorer (TopXp)

Sigrity’s Topology Explorer function is for signal and power topology exploration, you can evaluate signal integrity alone or analyze signals together with power. You can use complex connections of models (elements) and connect them to one transmitter/receiver/discrete element, as well as copy part of the drawn connection diagram and elements for further channel tuning. These features are included in the Sigrity Aurora software package, which has the ability to automatically extract circuits from a multilayer printed circuit board or chip package.

Sigrity SystemSI Serial Link Analysis (SLA)

Sigrity SystemSI SLA is a chip-to-chip signal path simulation solution for interfaces such as PCI Express (PCIe), HDMI, SFP+, Xaui, Infiniband, SAS, SATA, USB, and more. It is possible to pre-evaluate using transmitter and receiver model sets from various manufacturers, as Cadence works with chip designers to provide up-to-date product information. Using models of connectors, boards, you can achieve the closest analogue of your data transmission channel.

Simulation will help to predict crosstalk and the quality of the synchronization and data loss protection mechanisms, determine the channel quality parameters (number of lost bits, jitter and noise level).

Analysis of high-speed interfaces

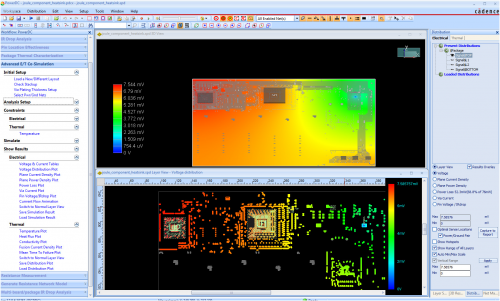

Sigrity Layout Workbench Parallel Bus Analysis (PBA)

PBA is a solution aimed at modeling parallel data transfer interfaces, such as DDRx, taking into account the non-ideal Power Distribution Network effects it various systems of a printed circuit assembly or block. You can create an interface model at the pre-routing stage, and then, after completing the layout, supplement it with data from layout to take into account the influence of the design, the location of the layers and adjacent conductors. Simulation can help you check for reflections, crosstalk, switching noise, and more.

PBA Advantages:

- Accurate simulation from DC to desired AC frequency

- Advanced channel simulation based on IBIS-AMI models

- Automatic eye diagram and U-curve generation for bit error rate (BER) determination.

- Reflection and crosstalk detection

- Accounting for simultaneous switching noise

- Settling and holding time measurement