Digital IC Design and Signoff from Cadence

In today’s rapidly evolving landscape, designs are growing in size and complexity. As a result, achieving the desired power, performance, and area (PPA) targets has become increasingly challenging. Furthermore, tight schedules further intensify the engineering task at hand. However, Cadence® has developed an integrated digital IC design full flow that addresses these difficulties by incorporating groundbreaking innovations that transcend the limitations of individual tools. By integrating core engines and key technologies, the Cadence digital full flow empowers customers to surpass their PPA objectives ahead of schedule.

Design Creation:

- Logic Equivalence Checking

- Functional ECO

- Low-Power Validation

- Synthesis

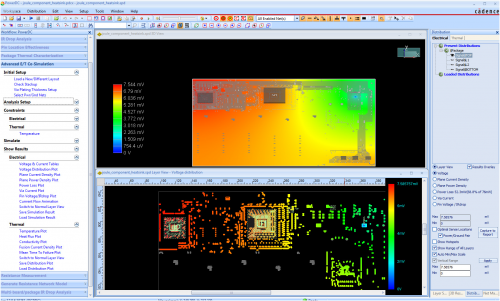

- Power Analysis

- Constraints and CDC Signoff

- Test

Implementation:

- Innovus Implementation and Floorplanning

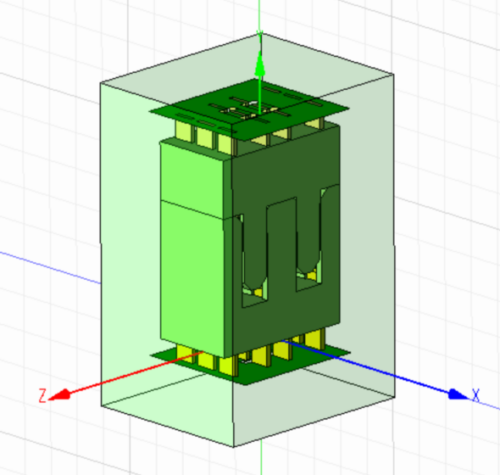

- Integrity 3D-IC

- Cadence Cerebrus Intelligent Chip Explorer

Signoff:

- Silicon Signoff and Verification

- Library Characterization

Technologies:

- 3D-IC Design

- Advanced Node

- Arm®-Based Designs

- Low Power

- Mixed-Signal Design

- AI / Machine Learning Solutions