Riviera-PRO

Verification platform

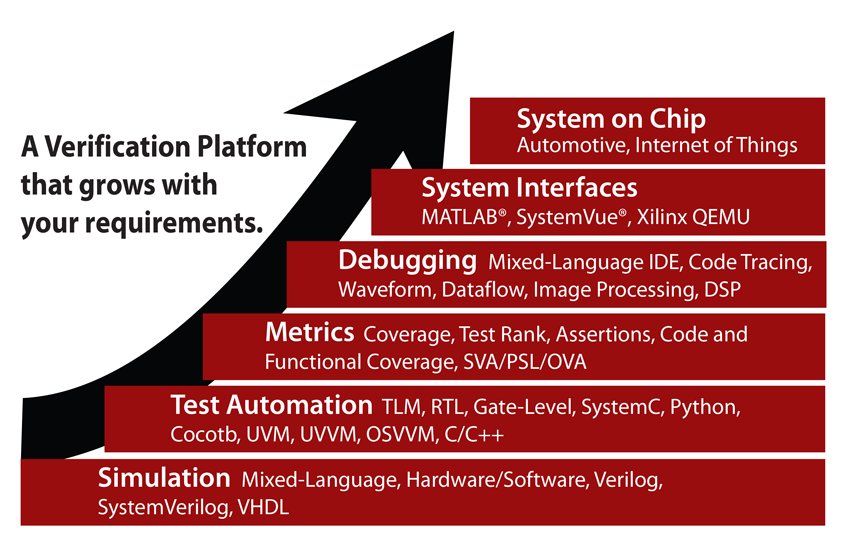

The ALDEC Riviera-PRO™ software product is designed to solve the problems of verifying analog-digital FPGAs and systems on a chip (SoC). Riviera-PRO provides a unique combination of efficiency, repeatability, and automation by combining a high-performance FPGA simulation engine, advanced debugging capabilities at various levels of abstraction, and support for modern standards in FPGA and ASIC programming languages and verification libraries.

Key Features and Benefits

High Performance Simulation

- Powerful simulation optimization algorithms.

- Market-leading simulation efficiency and capacity

- Support for the latest verification libraries, including Universal Verification Methodology (UVM)

Advanced Debugging

- Integrated multilingual debugging environment

- Tools: UVM Toolbox, UVM graph, Class Viewer, Transaction streams and data

- Built-in Debugging Tools

- Comprehensive validation based on SVA and PSL

- Advanced features for functional and code coverage analysis

- Efficient verification route with user-defined test plan linked to coverage database

- Chart and image viewer for visual representation of large amounts of data

Market-leading return on investment

- Riviera-PRO enables users of ALDEC products to develop innovative products in less time and at a lower cost

- Aldec products provide the integration you need to build complete development and verification flow

- Using of any Aldec product is accompanied by good customer support and trainings