Active-HDL – universal FPGA simulator

FPGA Simulator

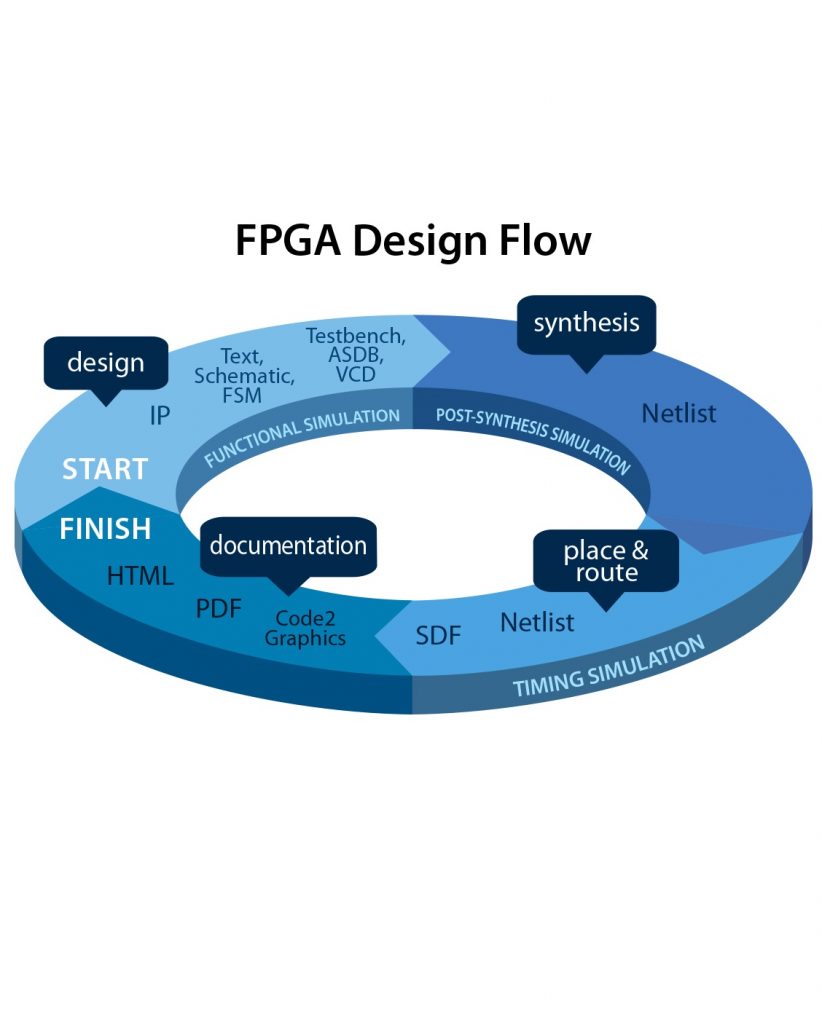

Active-HDL is an RTL design editor, a mixed RTL FPGA code simulator that includes: an industry-proven multilingual simulation engine for IEEE VHDL, Verilog® and SystemVerilog (Design), up to 2x faster relative to the standard simulators supplied for Xilinx or Intel (Altera) FPGAs. It provides support for encoded IP cores, without any restrictions on the size of the FPGA device. Using Active-HDL, your FPGA design team can speed up the process of developing FPGA firmware many times over, compared to using the simulators from Xilinx, Intel or Atmel. To verify the FPGA, you can additionally use another product from ALDEC – the FPGA verification program Riviera-PRO ™. You can check the quality of the RTL code in the ALINT-PRO™ software product.

You can download the Free Active-HDL Student Edition of charge to see the basic features of the product or to solve simple tasks with certain limitations.

You can also request the educational licenses that the ALDEC University Program provides.

Overview of FPGA development environment Active-HDL

User Reviews

“Simulation speed in Active-HDL is really better, i.e. faster than Vivado or Quartus…”

“Active-HDL editor is convenient, it has syntax highlighting and multi-selections inside. The whole project is beautifully divided into directory structure…”

“There is no need to wait for recompilation of all the source code, if something was changes in a single block of hierarchical project , unlike Vivado, where it is necessary to recompile the whole project…”

“Working with Active-HDL is much more convenient and efficient than, for example, using the Sublime + Vivado bundle…”

“Modelsim is just a simulator! And ALDEC Active-HDL is a very powerful design entry tool+simulator…”