Официальный дистрибьютор - ООО «ПСБ СОФТ» <a href="https://www.pcbsoft.ru">www.pcbsoft.ru</a> +7 (800) 333-97-22

### What is OrCAD DFM Checker?

- PCB analysis technology that identifies fabrication and manufacturing-centric design issues

- Powerful, yet easy-to-use, analysis for all design types from simple to complex

- Easily manages checks through rule sets that can be organized into layer types and sub-categories

Identify design issues that have the potential to lower yields and produce scrap

Ready

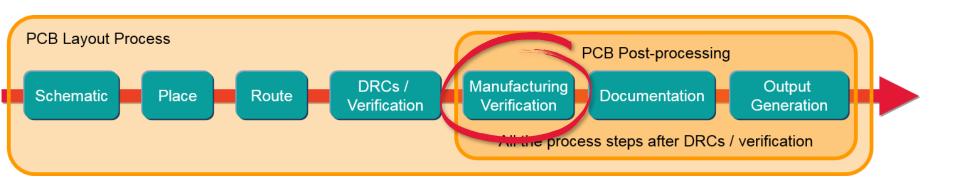

# Why Check for Manufacturing Issues?

- Increasing design complexity requires more specialized checking vs. traditional CAD tool DRCs

- Designs that pass standard DRCs may still contain issues that result in low manufacturing yields, or costly scrap

- Correcting fabrication issues can help reduce the amount of design modification done by the fabricator

- If the fabricator is modifying your design, you have lost database integrity

### **Key Features**

- Quickly locate defects that could result in PCB scrap

- Create and store checking routines for re-use on other designs

- Define areas to run differing analysis such as BGA areas on a standard board

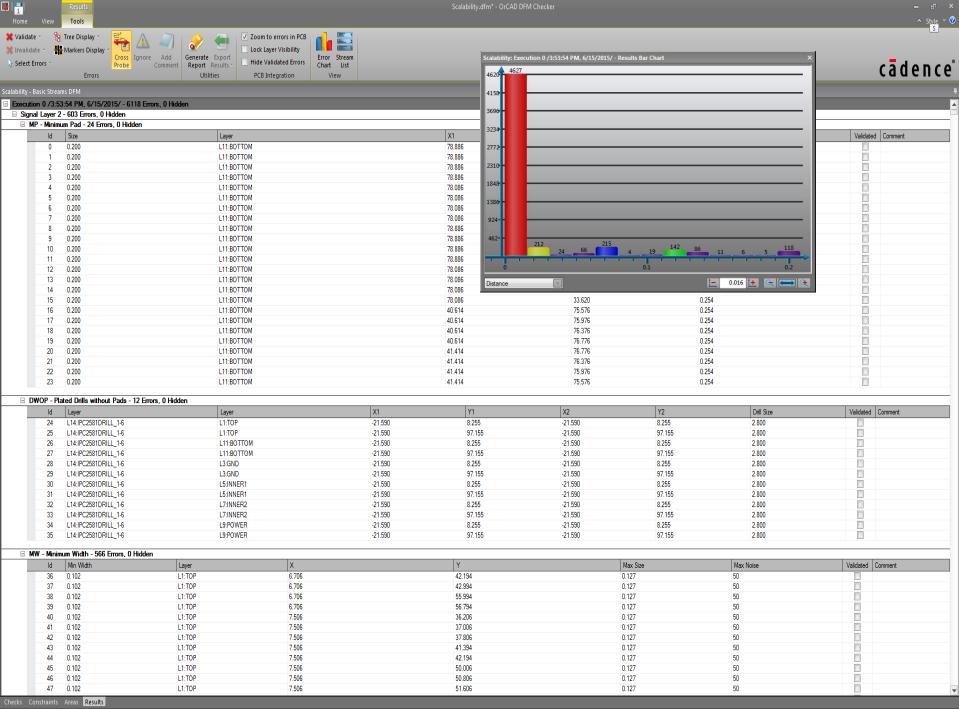

- Validate the results with charting and crossprobing

- Annotate errors for sharing of information in a design group

## Identity DFF / DFM Issues

- Quickly locate and correct defects that could result in low manufacturing / assembly yields or scrap

- Starved thermals

- Acid traps / slivers

- Missing traces

- Incorrect drilling

- Shorts resulting from layer merge

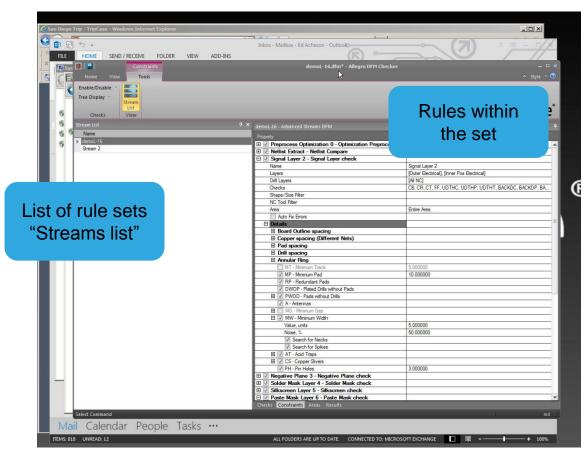

# Store and Reuse Checking Rule Sets

- Create rule sets that can be reused on other designs

- Rule sets by types of designs

- Rule sets by manufacturers capabilities

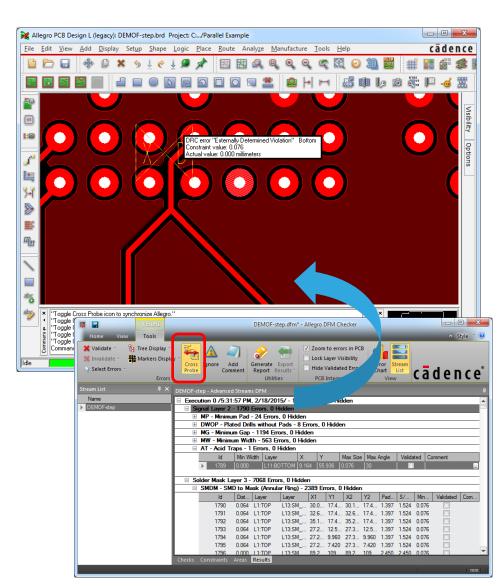

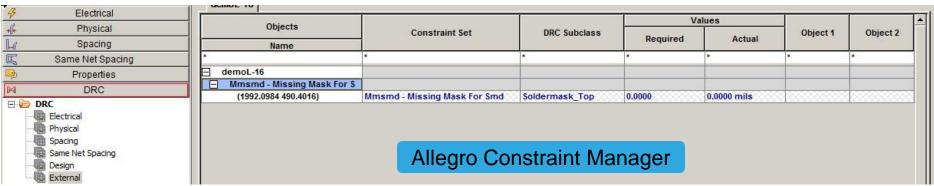

### Cross-probing between DFM checker and PCB Editor

- Constraints and constraint regions extracted by DFM Checker

- Automatically creates a default verification "stream"

- From the layer structure, constraints and constraint regions

- DRC markers added into PCB Editor

- Selection in the error lists in DFM Checker will zoom to the error location in PCB Editor

- Details shown through tooltip in PCB Editor

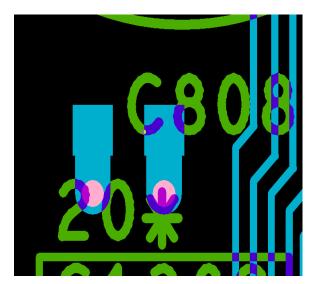

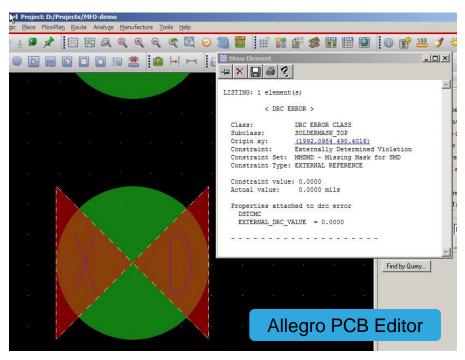

# Missing mask in PCB Editor

# CADENCE PCB SOLUTIONS